Toshiba Memory Corporation, el líder mundial en soluciones de memoria, anunció hoy el desarrollo de un chip de puente que realiza SSD de alta velocidad y gran capacidad. Usando chips de puente desarrollados con un área pequeña ocupada y bajo consumo de energía, la compañía ha logrado conectar más chips de memoria flash con menos líneas de señal de alta velocidad que con el método convencional de no chips de puente. Este resultado se anunció en San Francisco el 20 de febrero, en la Conferencia Internacional de Circuitos de Estado Sólido 2019 (ISSCC 2019).

En los SSD, varios chips de memoria flash están conectados a un controlador que administra su operación. A medida que se conectan más chips de memoria flash a una interfaz de controlador, la velocidad de operación se degrada, por lo que hay límites en la cantidad de chips que se pueden conectar. Para aumentar la capacidad, es necesario aumentar el número de interfaces, pero esto da como resultado una enorme cantidad de líneas de señal de alta velocidad conectadas al controlador, lo que dificulta la implementación del cableado en la placa SSD.

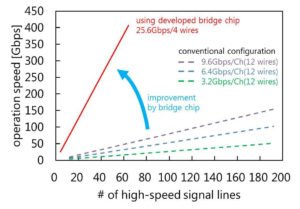

La compañía ha superado este problema con el desarrollo de un chip puente que conecta el controlador y los chips de memoria flash (Fig. 1), tres técnicas novedosas: una conexión en cadena tipo margarita que incluye el controlador y los chips puente en forma de anillo; una comunicación en serie utilizando PAM 4; y una técnica de mejora de jitter para eliminar un circuito PLL en los chips de puente. Al utilizar estas técnicas, la sobrecarga de los chips de puente se reduce, y es posible operar una gran cantidad de chips de memoria flash a alta velocidad con solo unas pocas líneas de señal de alta velocidad (Fig. 2).

La configuración en forma de anillo de los chips de puente y el controlador reduce el número de transceptores requeridos en el chip de puente de dos pares a un par, y logra la reducción del área de chip del chip de puente. Además, la adopción de la comunicación serie PAM 4 entre el controlador y los chips de puente en cadena de margarita reduce la velocidad de operación en los circuitos de los chips de puente y relaja el rendimiento requerido. Un nuevo CDR * 5 que utiliza las características de PAM 4 para mejorar las características de fluctuación elimina la necesidad de un circuito PLL en el chip de puente, que también contribuye a un área de chip más pequeña y un menor consumo de energía.

Los prototipos de chips de puente se fabricaron con un proceso CMOS de 28 nm, y los resultados se evaluaron mediante la conexión de cuatro chips de puente y un controlador en una cadena tipo margarita en forma de anillo. Esto confirmó el desempeño satisfactorio de la comunicación PAM 4 por parte de todos los chips de puente y el controlador a 25.6 Gbps, y también es posible obtener una BER * 6 de menos de 10-12.

En el futuro, la compañía continuará con el trabajo de desarrollo para lograr un almacenamiento de alta velocidad y gran capacidad a niveles que aún no se han visto al mejorar aún más el rendimiento del chip de puente al tiempo que reduce el área y el consumo de energía del chip.

Notas

- 1 cadena de margaritas: un esquema de conexión en el que múltiples chips se conectan en secuencia

- 2 PAM 4: Modulación de amplitud de pulso de 4 niveles (contiene datos de 4 valores)

- 3 Jitter: Fluctuación en el dominio del tiempo del reloj o formas de onda de señal

- 4 PLL: Phase Locked Loop (un circuito que genera una señal de referencia precisa)

- 5 CDR: Recuperación de datos del reloj (un circuito que recupera los datos y el reloj de la señal recibida)

- 6 BER: tasa de error de bits (el valor más bajo es el mejor rendimiento)